## 10G/25G UDP/IP Offload Engine

CT1012-UDP/IP - Product Brief - Version 2.1- February 2023

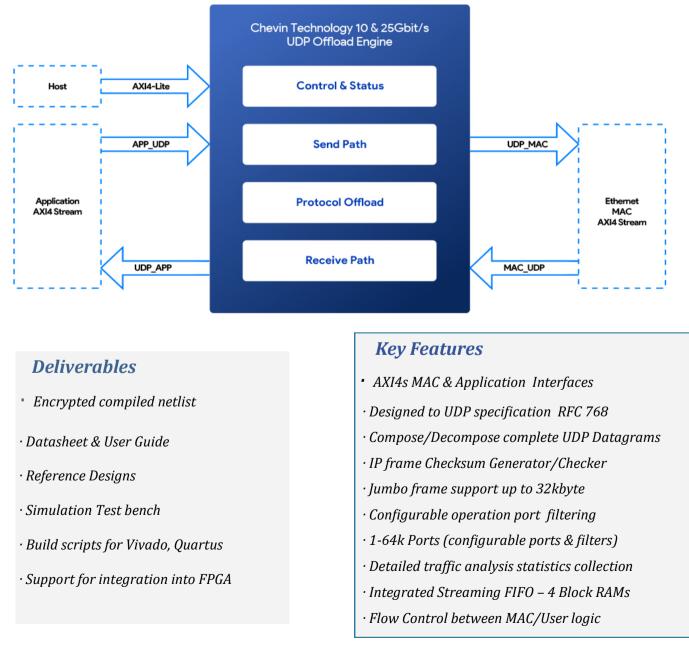

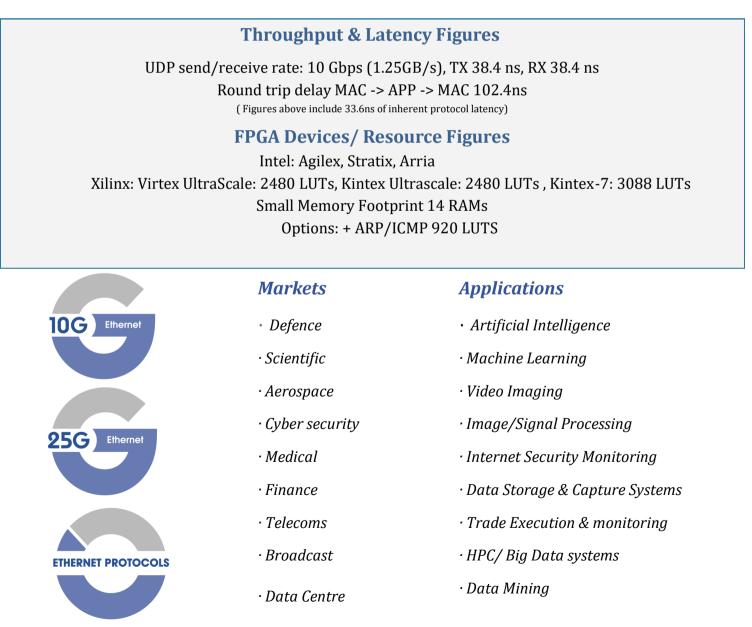

User Datagram Protocol (UDP/IP) is a communications protocol used for establishing connections between applications on the Internet. The UDP is a transport layer that runs on top of the Internet Protocol (IP) Layer. Chevin Technology's 10G & 25G UDP Ethernet IP core is an FPGA Synthesisable Offload Engine with Checksum Offload for ultra low-latency connectivity. The UDP/IP is configurable for Intel and Xilinx FPGAs, and simplifies integration by handling the complete Ethernet frame assembly. Chevin Technology's UDP/IP is a mature IP core with proven success in customers' projects. A simple AXI4 streaming interface is all that is required to start sending and receiving UDP datagrams, and only the user data payload is exchanged between the application and the UDP block. For a single port application the port number can be set to a constant, hard coded or software configurable. A multi- port application is supported by a single UDP/ IP core by using the TDEST sideband embedded in the streaming interface.

Chevin Technology Ltd., The Bradfield Centre, 184 Cambridge Science Park, Milton Road, Cambridge, Cambridgeshire, CB4 0GA, UKTelephone: +44 (0)1223 817009Email: ip@chevintechnology.comwww.chevintechnology.com

CT1012-XGUDP - Product Brief - Version 2.1 February 2023

Chevin Technology's UDP IP core offloads frame assembly with hardware accelerated checksum calculation for UDP datagrams. The application side FIFO provides independent TX/RX buffering and flow control between Application logic and UDP, over a streaming 64bit interface in a single clock domain. Remote port information is multiplexed with the streaming interface to provide a flexible solution for application logic.

A detailed statistics block provides a running count of frames sent and received , number of bytes sent/received, frames dropped due to flow control, last sent/received frame size and optional timestamp. Reference designs are available on selected boards using standard software development tools. The application side can connect directly to any 64bit MAC with an easy to use streaming AXI4s interface.

We recommend pairing the UDP/IP with Chevin Technology's MAC, an ultra-low-latency Ethernet MAC and other stack layers such as ICMP and ARP, for a more integrated FPGA solution.

Chevin Technology Ltd., The Bradfield Centre, 184 Cambridge Science Park, Milton Road, Cambridge, Cambridgeshire, CB4 0GA Telephone: +44 (0)1223 817009 Email: ip@chevintechnology.com www.chevintechnology.com