# ATUM A5 Board User manual

#### Contents

| Chap | ter 1 Overview               | 4 |

|------|------------------------------|---|

| 1.1  | General Description          | 4 |

| 1.2  | Board Layout                 | 5 |

| 1.3  | Key Features                 | 5 |

| 1.3. | Block Diagram                | 7 |

| 1.4. | Mechanical Specifications    | 7 |

| Chap | ter 2 Board Component        | 9 |

| 2.1  | Configuration Interface      | 9 |

| 2.2  | Setup and Status Components1 | 3 |

| 2.3  | Reset Devices                | 0 |

| 2.4  | Clock Circuit2               | 2 |

| 2.5  | General User I/O2            | 4 |

| 2.6  | 2x20 GPIO Expansion Header2  | 7 |

| 2.7  | Micro SD Card and eMMC2      | 9 |

| 2.8  | FMC+ Connector3              | 1 |

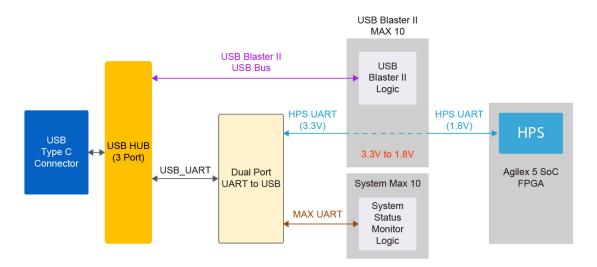

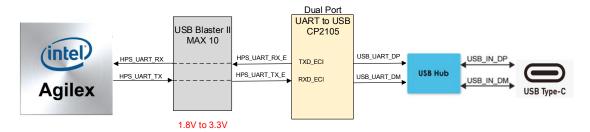

| 2.9  | USB to UART4                 | 8 |

| 2.10 | DDR4 SDRAM5                  | 1 |

| 2.11 | USB     |                                 | 57 |

|------|---------|---------------------------------|----|

| 2.12 | Gigabi  | t Ethernet                      | 59 |

| 2.13 | 2x6 GF  | PIO Header                      | 63 |

| 2.14 | QSFP-   | + Port                          | 64 |

| 2.15 | HDMI (  | Output Port                     | 67 |

| 2.16 | MIPI C  | Connector                       | 69 |

| 2.17 | PCI Ex  | rpress                          | 72 |

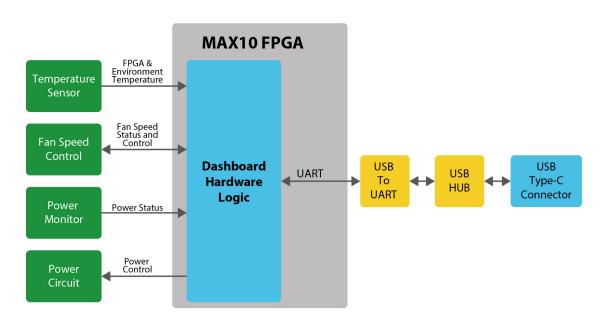

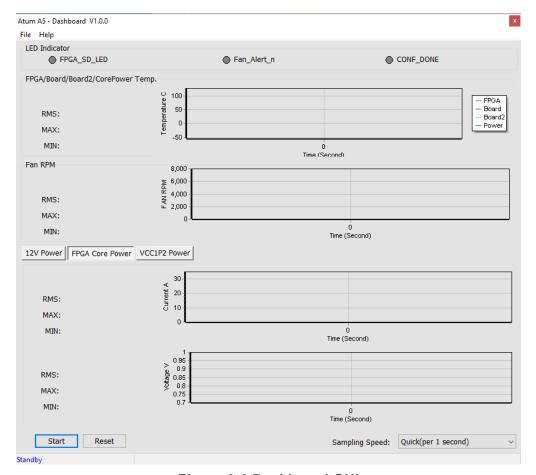

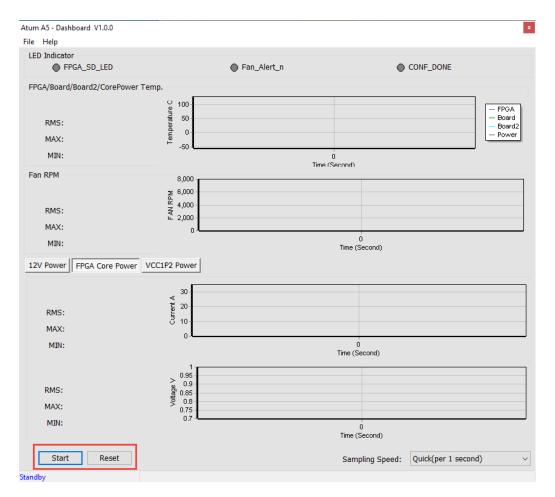

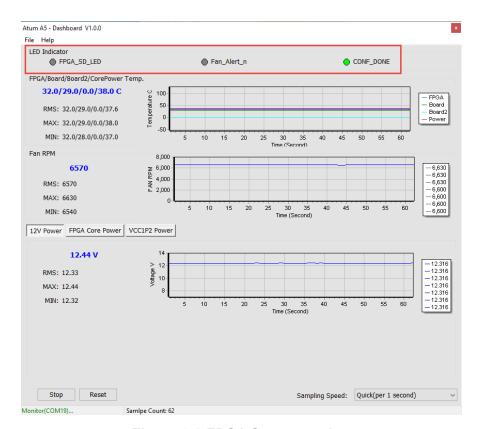

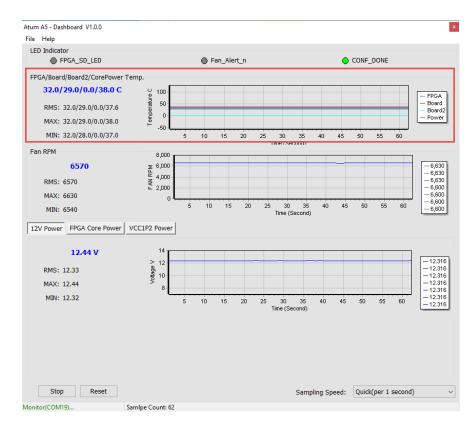

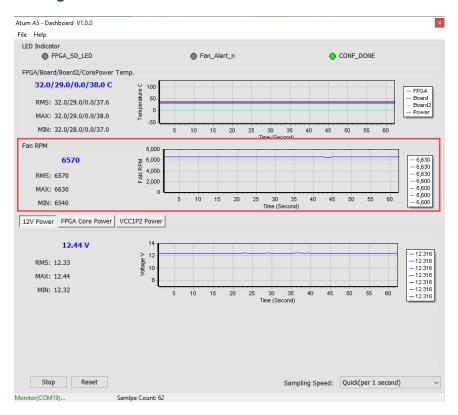

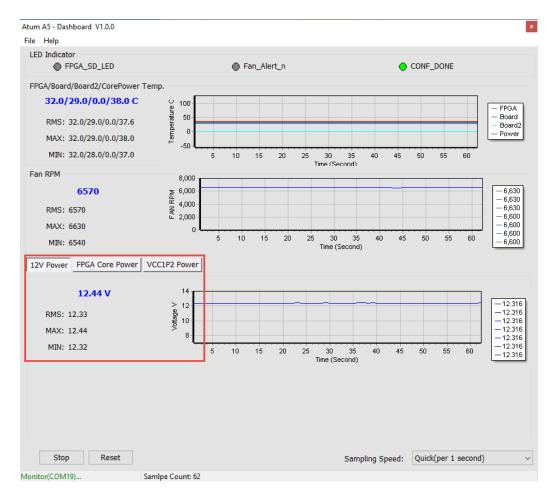

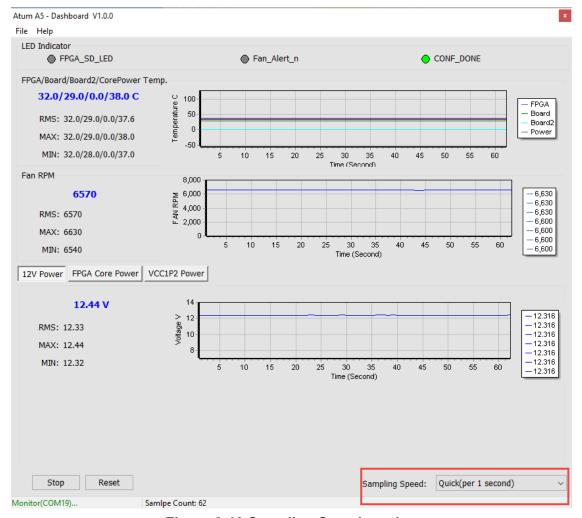

| Chap | ter 3   | Dashboard GUI                   | 76 |

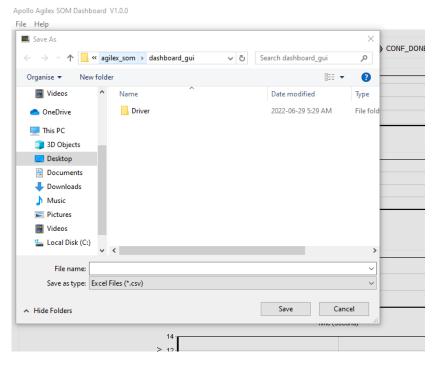

| 3.1  | Setup   | for the Dashboard GUI           | 76 |

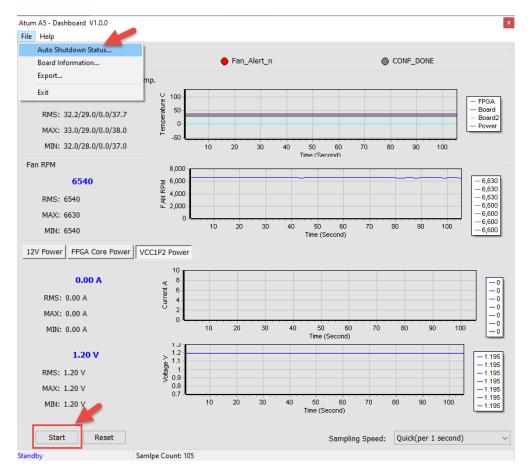

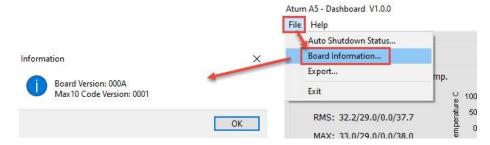

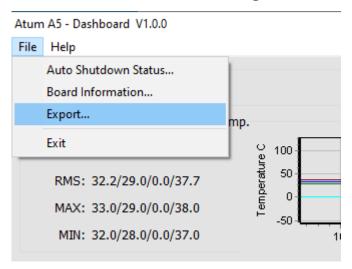

| 3.2  | Run Da  | ashboard GUI                    | 78 |

| Chap | tor 1   | In a tall Duir on fau tha Danud | 00 |

|      | ter 4   | Install Driver for the Board    | 00 |

| 4.1  |         | the USB Blaster II Driver       |    |

|      | Install |                                 | 88 |

| 4.2  | Install | the USB Blaster II Driver       | 88 |

# **Chapter 1**

# **Overview**

his chapter provides an overview of the Atum A5 Development Kit and installation guide.

# 1.1 General Description

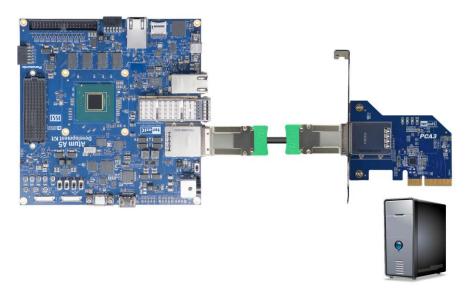

The Atum A5 Development Kit is Terasic's first development kit in the Intel® Agilex™ 5 FPGA portfolio. Powered by the largest Agilex® 5 SoC FPGA with 656K LEs, the Atum A5 Development Kit is an out-of-the-box platform for advanced AI and vision application development.

With a rich set of interfaces ranging from 2.5G Ethernet, high-speed DDR4, QSFP+, PCIe Gen 3x4, FMC+ connectors, to MIPI connector and HDMI, the Atum A5 excels in a wide range of applications, including industrial networking, AI, embedded vision, medical and healthcare, video applications, and various other I/O expansion and high-speed applications!

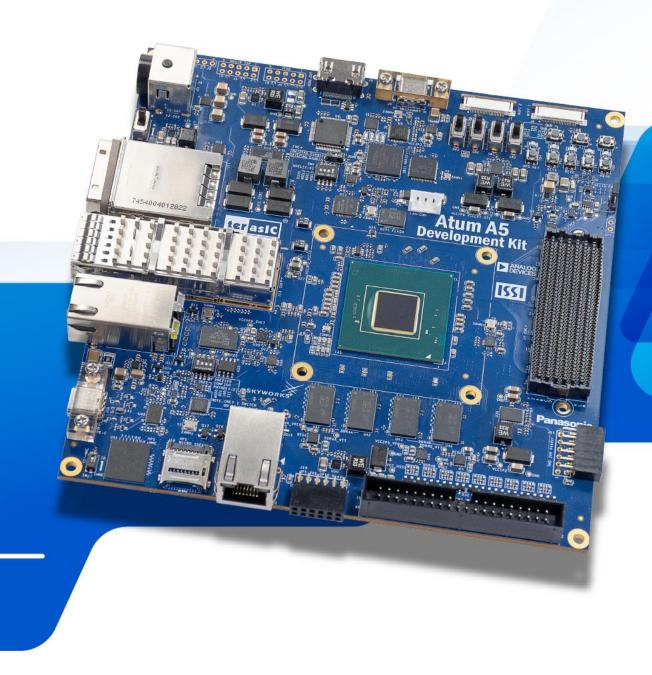

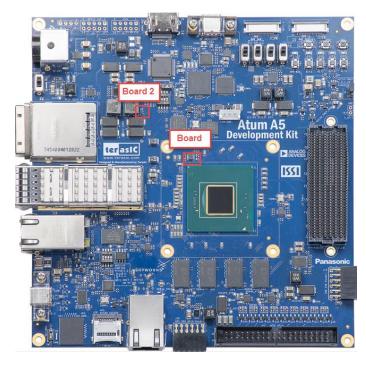

Figure 1-1 Atum A5 board with heat sink and fan

# 1.2 Board Layout

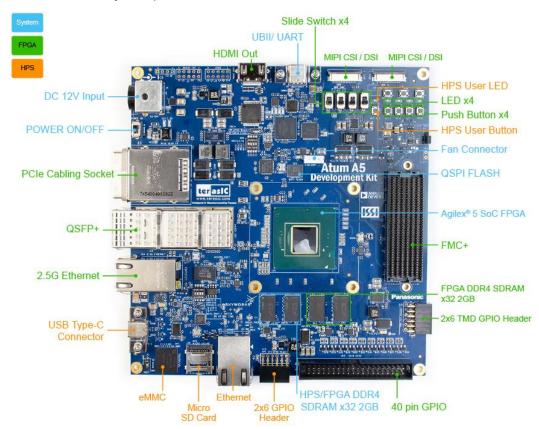

The figures below depict the layout of the board and indicate the location of the connectors and key components.

Figure 1-2 Atum A5 board top

# 1.3 Key Features

The following hardware is implemented on the Atum A5 board:

#### **■** FPGA Device

- Intel® Agilex™ 5 SoC FPGA : A5ED065BB32AE4SR0

- 650K logic elements (LEs)

- 31.46 Mbits embedded memory(M20K)

- 24 transceivers (up to 17.16Gbps)

- 11,520 18-bit x 19-bit multipliers

- 1692 DSP blocks

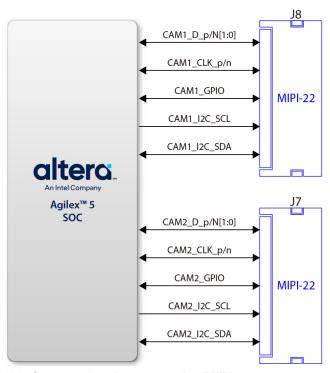

- MIPI D-PHY v2.5

**User Manual**

Atum A5

#### **FPGA Configuration**

- On-Board USB Blaster II (UB2) for FPGA programming and Debug

- Support ASx4 Configure Mode with 512Mbits QSPI Flash

#### **FPGA Fabric**

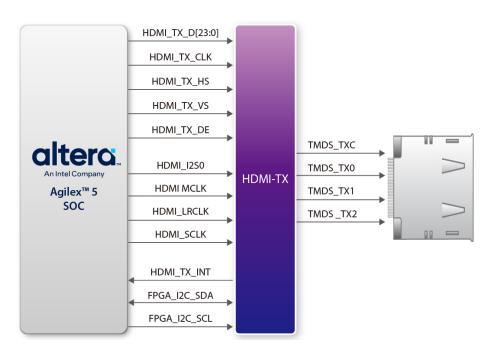

- HDMI Output Port (Support 1080P)

- DDR4-A: 2GB DDR4 with 32-bit data bus (no ECC). Shared with HPS

- DDR4-B: 2GB DDR4 with 32-bit data bus (no ECC)

- One FMC+ connector with 16 transceivers

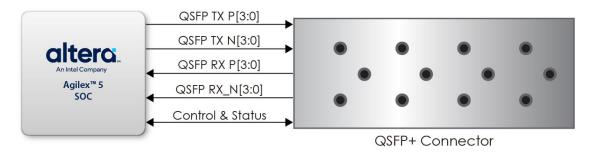

- One QSFP+ Port for 40 GbE network interface

- One 2.5G Ethernet Port

- Two 2-lanes MIPI Connector for Camera/Display

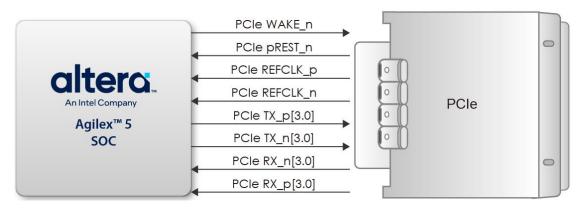

- One PCIe Calbing Gen3 x4 Socket

- One 3.3V 2x20 DE-GPIO Header

- One 3.3V 2x6 TMD Header

- User LED x4, Button x4, DIP Switch x4

#### **HPS(Hard Processor System) Fabric**

- MicroSD Socket and 8GB eMMC

- DDR4-A: 2GB DDR4 with 32-bit data bus (no ECC). Shared with FPG

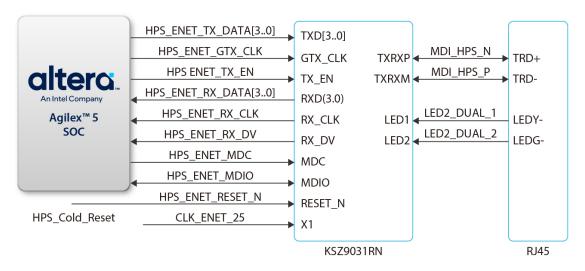

- Gigabit Ethernet PHY + RJ45

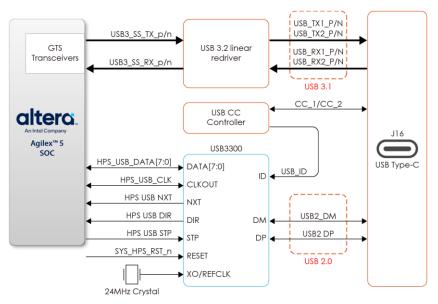

- USB 3.1 Gen1 (5Gbps; use 1 transceiver) with USB Type-C connector

- UART to USB Port

- LED x1, Button x1, Cold Reset Button

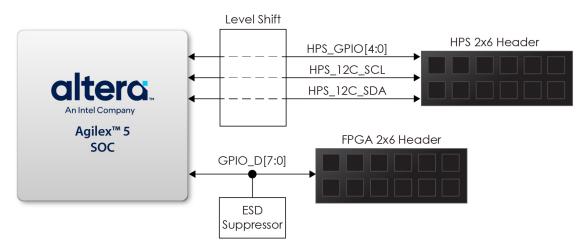

- One 3.3V 2x6 GPIO Header. Including One I2C Bus

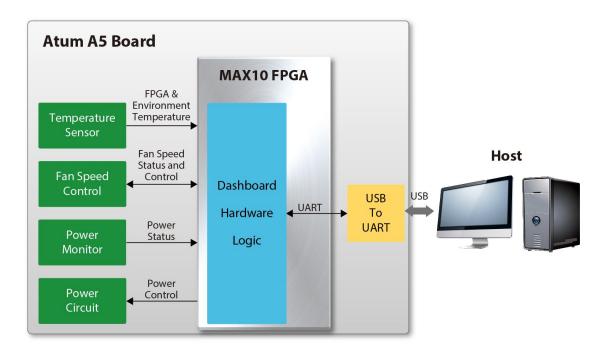

#### **Dashboard System**

- **Power Monitor**

- Temperature Monitor

- Auto Fan Control

# 1.3. Block Diagram

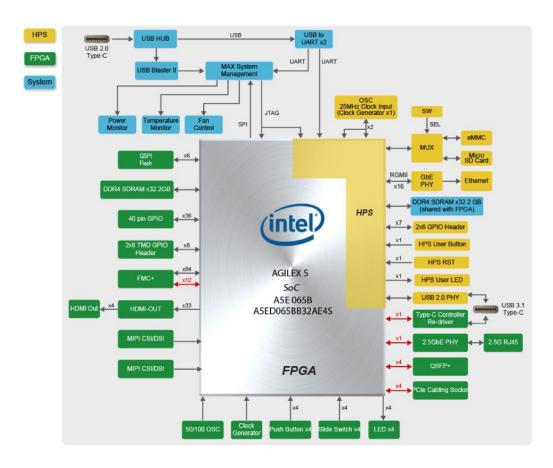

**Figure 1-3** shows the block diagram of the Atum A5 board. To provide maximum flexibility for the users, all key components are connected to the Agilex® SoC FPGA device. Thus, users can configure the FPGA to implement any system design.

Figure 1-3 Block diagram of the Atum A5 board

# 1.4. Mechanical Specifications

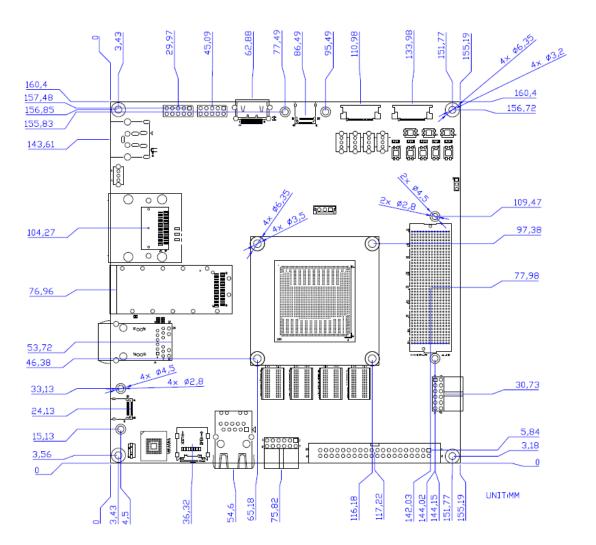

**Figure 1-4** shows the Mechanical Layout of Atum A5 board. The unit of the Mechanical Layout is millimeter (mm).

Figure 1-4 Mechanical layout

8

# **Chapter 2**

# **Board Component**

his chapter introduces all the important components on the Atum A5.

# 2.1 Configuration Interface

This section describes the configuration mode for Agilex SoC FPGA available on the Atum A5. The peripheral circuits and usage scenarios for each mode will be listed.

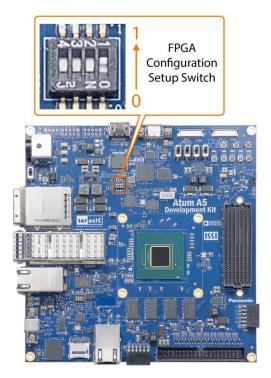

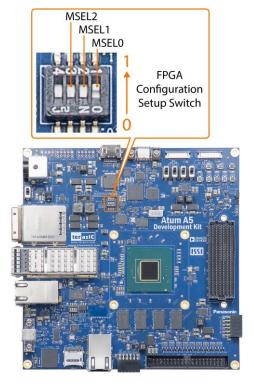

As shown in **Figure 2-1**, the mode select pin of the FPGA on the Atum A5 board has been set to **Active Serial (AS) Fast mode** using **FPGA Configure Setup Switch** (**SW4**), For detailed about SW4, please refer to section 2.2 : *FPGA Configure Setup Switch* part. Thus, the Atum A5 board supports the following configuration modes:

- JTAG Mode (Configure the FPGA using the on-board USB Blaster II).

- Active Serial (AS) Fas mode

Users can use these modes to configure the FPGA or HPS (Hardware Process System) fabric in the Agilex SoC FPGA and make the FPGA to run the user's logic or boot the HPS to run the OS.

Below we will introduce more detailed information of AS mode, as well as other configuration information.

Figure 2-1 The MSEL pin setting

#### ■ Active Serial (Fast) mode

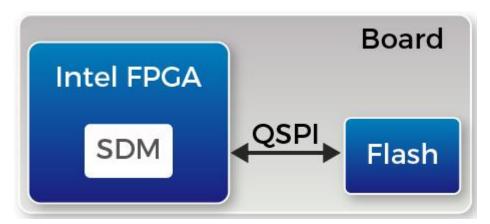

In AS mode, the FPGA's configuration file is stored in the QSPI flash. The Secure Device Manager (SDM) in Agilex SoC FPGA is responsible for the entire AS mode process and interface. The SDM will load the initial configuration firmware from the QSPI flash to configure the FPGA including FPGA I / O and core configuration. HPS part of the boot can also be completed in this mode. **Figure 2-2** shows the architecture of the AS mode of the Atum A5 board.

Figure 2-2 AS mode for the Atum A5 board

For more information on the configuration of Agilex SoC FPGAs, please refer to the file: <u>Device Configuration User Guide: Agilex™ 5 FPGAs and SoCs</u>

#### ■ SoC FPGA boot

The boot process for Agilex SoC FPGA can be divided into two different methods:

- FPGA Configuration First Mode

- HPS Boot First Mode

The difference between the two methods is the initial difference between HPS and FPGA fabric after powering on. More details can be found in the user documentation: Hard Processor System Booting User Guide: Agilex 5 SoCs.

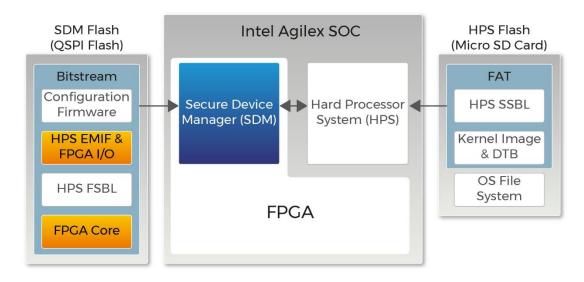

The factory setting of the SoC boot of the Atum A5 board is the **FPGA Configuration First Mode**. The architecture is shown in the **Figure 2-3**. Two storage mediums are used. The system needs QSPI flash on Atum A5 as SDM flash for booting.

Figure 2-3 FPGA Configuration First Dual SDM and HPS Flash

The QSPI flash memory has the following boot data for the first part of the SoC FPGA configuration:

- Configuration firmware for the SDM

- FPGA I/O and HPS external memory interface (EMIF) I/O configuration data

- FPGA core configuration data

- HPS First-Stage Boot Loader(FSBL) code and FSBL hardware handoff binary data

Meanwhile, Terasic provides the micro SD card with built-in image data as HPS flash, which is used for HPS boot in the later part. The micro SD card stores the following data:

- Second-Stage Boot Loader(SSBL)

- Kernel Image and Device Tree Blob(DTB)

- Operating System

The factory SoC boot process of Atum A5 is summarized as follows:

When the Atum A5 board is powered on, the SDM will read the configuration firmware and complete SDM initial form the QSPI flash according to the MSEL pin setting. Then, the SDM will configure the FPGA I/O and core (full configuration).

After the FPGA is first configured, SDM continues to load the FSBL(First-Stage Boot Loader) from the QSPI flash and transfer it to the HPS on-chip RAM, and releases the HPS reset to let the HPS start using the FSBL hardware handoff file to setup the clocks, HPS dedicated I/Os, and peripherals.

The FSBL then loads the SSBL(Second-Stage Boot Loader) from the Micro SD Card into HPS SDRAM and passes the control to the SSBL. The SSBL enables more advanced peripherals and loads OS into SDRAM.

Finally, the OS boots and applications are scheduled for runtime launch.

### JTAG Programming

The JTAG interface of the Atum A5 is mainly implemented by the USB Blaster II circuit on the board. For programming by on-board USB Blaster II, the following procedures show how to download a configuration bit stream into the Agilex SoC FPGA:

- Make sure that power is provided to the FPGA board

- Connect your PC to the FPGA board using a micro-USB cable and make sure the USB Blaster II driver is installed on the PC.

- Launch Quartus Prime programmer and make sure the USB Blaster II is detected.

- In Quartus Prime Programmer, add the configuration bit stream file (.sof),

check the associated "Program/Configure" item, and click "Start" to start

# 2.2 Setup and Status Components

This section will introduce the use of the switch for setup on the Atum A5 board, as well as a description of the various status LEDs.

#### ■ Status LED

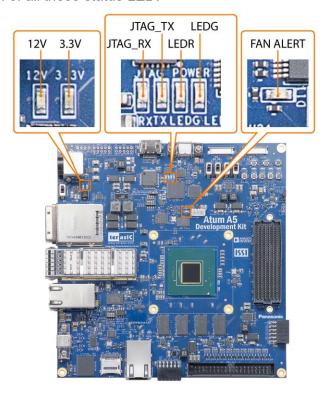

The FPGA development board includes board-specific status LEDs to indicate board status. Please refer to **Table 2-1** for the description of the LED indicators. **Figure 2-4** shows the location of all these status LED.

Figure 2-4 Position of the status LED

Table 2-1 Status LED

| Board<br>Reference | LED Name       | Description                                                                                 |

|--------------------|----------------|---------------------------------------------------------------------------------------------|

| D11                | FAN(FAN_ALERT) | Illuminates when the fan is abnormal, such as when the fan speed is different from expected |

| D9                 |                | Illuminates when 12-V power is active.                                                      |

**User Manual**

| D10 | 3.3V(3.3-V Power) | Illuminates when 3.3-V power is active.                                                                                                                                                                                                                                                                                                                                                                |  |  |

|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| D6  | JTAG TX           | Illuminates when the USB Blaster II circuit is transmitting data                                                                                                                                                                                                                                                                                                                                       |  |  |

| D5  | JTAG RX           | Illuminates when the USB Blaster II circuit is receiving data                                                                                                                                                                                                                                                                                                                                          |  |  |

| D8  | POWER LEDG        | Illuminates when the 3.3V power good and power sequence process finished.                                                                                                                                                                                                                                                                                                                              |  |  |

| D7  | POWER_LEDR        | <ol> <li>Illuminates when the 3.3V power abnormal or power sequence process failed.</li> <li>LED will blink when the following situations occur: (i) the FPGA temperature on the board temperature exceeds 95 degrees. (ii) the power consumption exceeds 160W. (iii) when the current of VCC_CORE exceeds 100A. Also, all the power of the FPGA will be cut off when this LED is blinking.</li> </ol> |  |  |

### ■ FPGA Configure Setup Switch

Apollo-Agilex SoM

**User Manual**

The **SW4** switche (see **Figure 2-6**) are used to specify the configuration mode of the FPGA. As currently only AS Fast and JTAG mode are supported. If SW4 is set to AS fast mode. When the board power up, the Secure Device Manager (SDM) in the FPGA will boot from the Quad SPI flash.

Figure 2-5 Position of slide switch SW4 for FPGA Configuration Mode

Table 2-2 MSEL Settings for supported configuration Scheme of the board

| FPGA Configuration<br>Mode | MSEL2 | MSEL1 | MSEL0 |

|----------------------------|-------|-------|-------|

| AS Fast (Default)          | 0     | 0     | 1     |

| JTAG                       | 1     | 1     | 1     |

#### **■** FMC+ JTAG Interface Switch

The JTAG interface switch **SW31** is to set whether the JTAG interface of the FMC + connector is connected to the JTAG chain in the Atum A5 board. The FMC+ connector will **not** be included in the JTAG chain if the switche is set to **ON** position (See **Figure 2-6**). **Table 2-3** lists the setting of the SW31. Note, if the user turns the position on SW31 to the OFF position, but does not connect the JTAG device on the FMC+ connector. The JTAG chain on the Atum A5 board will not be able to form a closed loop and Quartus will not be able to detect the FPGA device.

Figure 2-6 Position of slide switches SW3

Table 2-3 SW4 setting

| Board<br>Reference | Signal Name        | Description                                                               | Default |

|--------------------|--------------------|---------------------------------------------------------------------------|---------|

|                    |                    | ON: Bypass the JTAG interface of the FMC+ connector into the JTAG         |         |

| SW31               | FMCP_JTAG_BYPASS_n | chain  OFF: Enable the JTAG interface of the FMC+ connector into the JTAG | ON      |

|                    |                    | chain                                                                     |         |

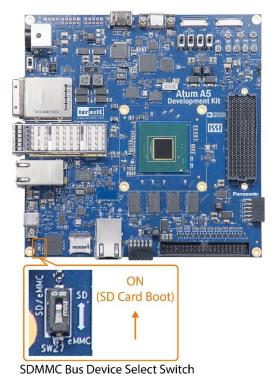

#### ■ SDMMC Bus Device Select Switch

The board provides Micro SD Card and on-board eMMC interface for HPS fabric in the FPGA. Users can choose one of them for HPS boot/data/system storage. The switch **SW27** on the board can help the user select which device (Micro SD Card or eMMC) will be used for HPS fabric. **Figure 2-7** shows the position of the SW27. **Table 2-4** list the setting for the JP1

Figure 2-7 Position of slide switches SW27

Table 2-4 SW27 setting

| Board<br>Reference | Signal Name | I Name Description                                                                        |    |  |  |  |

|--------------------|-------------|-------------------------------------------------------------------------------------------|----|--|--|--|

| SW27               | EMMC SEL    | ON: Select SD Card as the storage device for HPS fabric.  OFF: Select eMMC as the storage | ON |  |  |  |

|                    |             | device for HPS fabric                                                                     |    |  |  |  |

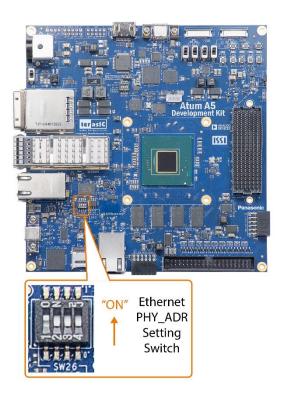

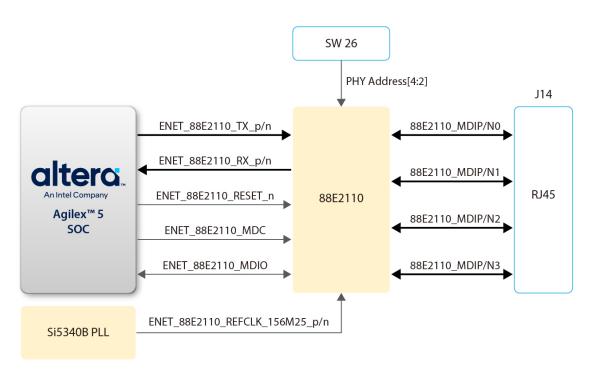

### ■ Ethernet PHY\_ADR Setting Switch

The **SW26** switches are used to set bit4~2 of the PHY address(**PHYAD[4:2]**) for the 2.5G Ethernet PHY (Marvell 88E2110). SW26 has a total of four switches, each switch represents a group of PHYAD [4:2] setting value. **Note that only one switch can be set to the on position at a time**. **Figure 2-8** shows the position of this switch on the board. **Table 2-5** list the setting for each switch.

Figure 2-8 Position of slide switches SW26

Table 2-5 SW26 setting

| Board<br>Reference | Description                                                     | Default |

|--------------------|-----------------------------------------------------------------|---------|

| SW26.1             | ON: Selects 000 for PHYAD[4:2] OFF: Deselect 000 for PHYAD[4:2] | ON      |

| SW26.2             | ON: Selects 001 for PHYAD[4:2] OFF: Deselect 001 for PHYAD[4:2] | OFF     |

| SW26.3             | ON: Selects 010 for PHYAD[4:2] OFF: Deselect 010 for PHYAD[4:2] | OFF     |

| SW26.4             | ON: Selects 111 for PHYAD[4:2] OFF: Deselect 111 for PHYAD[4:2] | OFF     |

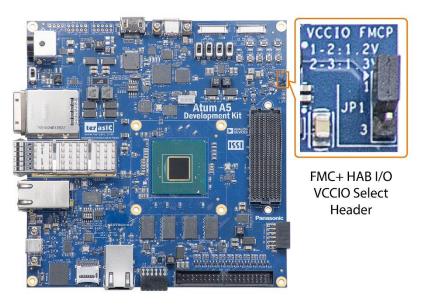

#### **FMC+ HAB VCCIO Select Header**

Apollo-Agilex SoM

**User Manual**

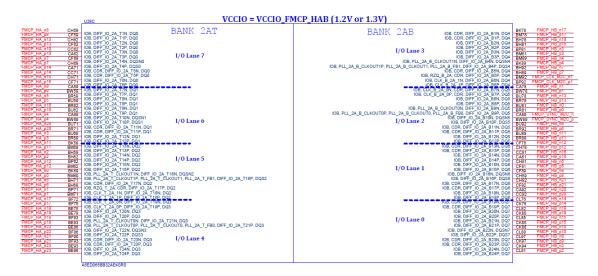

Some of the FPGA pin's I/O standard connected with the HPC (High Pin Count) part of the FMC+ connector can be set to voltages: 1.2V or 1.23V (See Figure 2-9 and Table 2-6). This function can be achieved because the VCCIO power pin of the FPGA bank where these FPGA I/Os are located can adjust the input voltage through the 3 pin

header (**JP1**). **Figure 2-10** shows the position of the JP1. **Table 2-7** list the setting for the JP1, user can short 2 pins of the header to modify the voltage level of the VCCIO\_FMCP\_HAB.

Figure 2-9 HPC FMC+ pin of the FPGA Bank 2AT/2AB

Table 2-6 FPGA I/Os on the FMC+ connector which can be changed I/O standard to 1.2 or 1.3V

| FMC Pins which can  |  |  |  |  |

|---------------------|--|--|--|--|

| modify I/O stadnard |  |  |  |  |

| FMCP_HA_p[230]      |  |  |  |  |

| FMCP_HA_n[230]      |  |  |  |  |

| FMCP_HB_p[210]      |  |  |  |  |

| FMCP_HB_p[210]      |  |  |  |  |

| FMCP_CLK_M2C_p[10]  |  |  |  |  |

| FMCP_CLK_M2C_n[10]  |  |  |  |  |

| FMCP_SYNC_M2C_p     |  |  |  |  |

| FMCP_SYNC_M2C_n     |  |  |  |  |

Figure 2-10 FMC+ HAB I/O standard setting headers

Table 2-7 JP1 Setting for FMC+ I/O standard

| JP3 Setting | FMC I/O Standard |

|-------------|------------------|

| JP1 3       | 1.2V (Default)   |

| JP1 3       | 1.3V             |

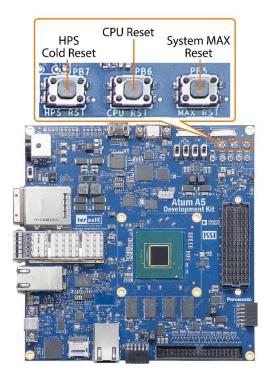

### 2.3 Reset Devices

The board provides 3 reset buttons for different system reset situations (see **Figure 2-11**). These buttons can reset FPGA, System MAX, HPS and FPGA respectively. Please refer to the following **Table 2-8** for details.

Figure 2-11 Rest devices of the board

Table 2-8 Reset Devices Pin Assignments, Schematic Signal Names, and Functions

| Part<br>Number | Schematic<br>Signal Name | I/O<br>Standard | FPGA Pin<br>Number | Application                                                                    |

|----------------|--------------------------|-----------------|--------------------|--------------------------------------------------------------------------------|

| PB6            | CPU_RESET_n              | 3.3-V<br>LVCMOS | PIN_ BF104         | This button can<br>be used for rest<br>FPGA (Need<br>user setting or<br>logic) |

| PB5            | MAX_RESET_n              |                 |                    | For resetting System MAX10                                                     |

| PB7            | HPS_COLD_RESET_N         |                 |                    | For resetting System HPS Fabric                                                |

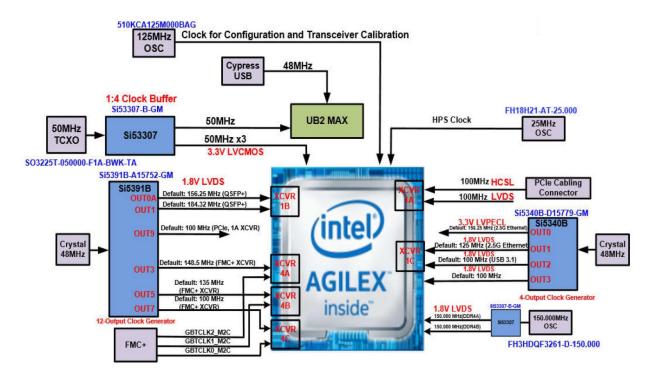

#### 2.4 Clock Circuit

The development board includes a 50 MHz TCXO, a 125 MHz OSC, a 150Mhz OSC and two programmable clock generators. **Figure 2-12** shows the default frequencies of on-board all external clocks going to the Agilex SoC FPGA.

Figure 2-12 Clock circuit of the FPGA Board

A clock buffer is used to duplicate the 50 MHz TCXO output clock, so there are three 50MHz clocks fed into different FPGA banks.

One of the programming clock generator (Si5391B) with ultra low-jitter clock outputs are used to provide special and high-quality clock signals for high-speed transceivers. Through I2C serial interface, the clock generator controllers in the Agilex SoC FPGA can be used to program the Si5391B to generate FMC+ connector, QSFP+ and PCIe reference clocks.

The other programming clock generator (Si5340B) is used to provide a high-speed differential clock source for the Ethernet and USB3.1 interfaces on the board. Users can also modify the output frequency through the I2C interface.

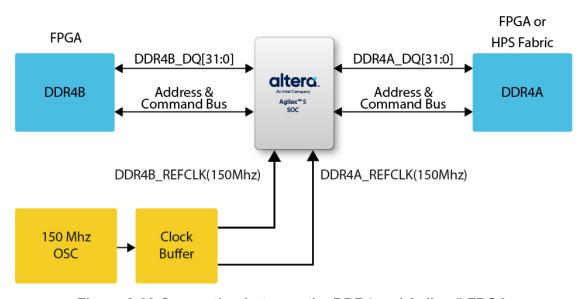

For memory interface, the board provides a 150Mhz clock and fan out it to two

different clocks to the Agilex FPGA via clock buffer (Si53307). The two clocks are used for the reference clock of the two group of the on-board DDR4 SDRAM.

One oscillator provides a 125 MHz clock used as configuration or used as the clock for transceiver calibration. Besides, there is one 25 MHz clock source to use as the HPS input clock.

Table 2-9 Clock source and clock pin to the FPGA

| Source   | Schematic<br>Signal Name       | Default<br>Frequency | I/O Standard     | FPGA Pin<br>Number | Application   |

|----------|--------------------------------|----------------------|------------------|--------------------|---------------|

|          | CLK_50_B5A                     |                      | 3.3V             | PIN_BF68           | User          |

|          | 0212022011                     |                      |                  |                    | application   |

| U29      | CLK_50_B6A                     | 50.0 MHz             | 3.3V             | PIN_CH128          | User          |

| Si53307  | -11-1                          |                      |                  |                    | application   |

|          | CLK_50_B6C                     |                      | 3.3V             | PIN_BP22           | User          |

|          | 331_33_33                      |                      |                  |                    | application   |

|          |                                |                      |                  |                    | Clock for     |

|          |                                |                      |                  |                    | configuration |

| Y8 OSC   | OSC_CLK_1                      | 125 MHz              | 1.8V             | PIN_BR102          | and           |

|          |                                |                      |                  |                    | transceiver   |

|          |                                |                      |                  |                    | calibration   |

| Y10 OSC  | DDR4A_REFCLK_p  DDR4B_REFCLK_p | 150 Mhz<br>150 Mhz   | True             | PIN_AB117 PIN_AC68 | DDR4A         |

| and      |                                |                      | Differential     |                    | reference     |

| U34      |                                |                      | Signaling        |                    | clock         |

| Clock    |                                |                      | True             |                    | DDR4B         |

| Buffer   |                                |                      | Differential     |                    | reference     |

|          |                                |                      | Signaling        |                    | clock         |

|          | ENET_88E2110_REFCLK_125M_p     |                      | High Speed       | PIN_AT13           | 2.5G          |

|          |                                | 125MHz               | Differential I/O |                    | Ethernet      |

|          |                                |                      |                  |                    | Interface     |

| U23      |                                |                      |                  | PIN_AP120          | HPS           |

| Si5340B  | HPS_USB3_REFCLK_100M_p         | 100Mhz               | CML              |                    | USB3.1        |

| 0100-100 |                                |                      |                  |                    | Interface     |

|          |                                |                      | True             | PIN_BF68           | User          |

|          | CLK_100_B2B_p                  | 100 Mhz              | Differential     |                    | application   |

|          |                                |                      | Signaling        |                    | арріїоціон    |

|         |                     |               |              |           | FMC+        |

|---------|---------------------|---------------|--------------|-----------|-------------|

|         | FMCP REFCLK0 p      | 148.5 MHz     | Differential | PIN_AT16  | connector   |

|         | r mor _rter oerto_p | 140.0 1011 12 |              |           | reference   |

|         |                     |               |              |           | clock 0     |

|         | FMCP_REFCLK1_p      | 135 MHz       | Differential | PIN_AY16  | FMC+        |

|         |                     |               |              |           | connector   |

|         |                     |               |              |           | reference   |

|         |                     |               |              |           | clock 1     |

|         | FMCP_REFCLK2_p      | 100 MHz       | Differential | PIN_BC29  | FMC+        |

| U57     |                     |               |              |           | connector   |

| Si5391B |                     |               |              |           | reference   |

|         |                     |               |              |           | clock 2     |

|         |                     | 156.25 MHz    | Differential | PIN_AV120 | QSFP port   |

|         | QSFP_REFCLK_p       |               |              |           | reference   |

|         |                     |               |              |           | clock       |

|         | CIPRI_REFCLK_p      | 184.32 MHz    | Differential | PIN_AY120 | CIPRI clock |

|         |                     |               |              |           | PCIe on-    |

|         | DOLE OF DELCTIV     | 100 MH=       | Differential | PIN_BC111 | board       |

|         | PCIE_OB_REFCLK_p    | 100 MHz       |              |           | reference   |

|         |                     |               |              |           | clock       |

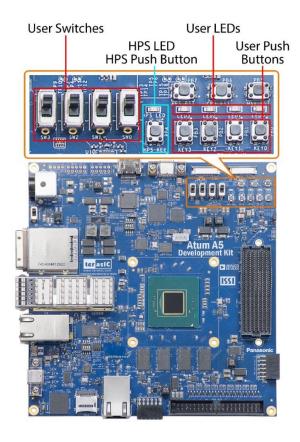

# 2.5 General User I/O

This section describes the user I/O interface of the FPGA and HPS fabric. Please note that the HPS and FPGA portions of the device each have their own pins. Pins are not freely shared between the HPS and the FPGA fabric. **Figure 2-13** shows the position of all these components and interface.

Figure 2-13 Position of all the general user components

#### ■ User Defined Push-buttons

Apollo-Agilex SoM

**User Manual**

The FPGA board includes four FPGA and one HPS fabric user defined push-buttons that allow users to interact with the Agilex SoC device. Each push-button provides a high logic level or a low logic level when it is not pressed or pressed, respectively. **Table 2-10** lists the board references, signal names and their corresponding Agilex SoC device pin numbers for the push-buttons of the FPGA. **Table 2-11** list the information of the push-button for the HPS fabric.

Table 2-10 Push-button (FPGA) Pin Assignments, Schematic Signal Names

| Board   | d   | Schematic   | Description                                     | I/O      | FPGA Pin |

|---------|-----|-------------|-------------------------------------------------|----------|----------|

| Referer | псе | Signal Name | Description                                     | Standard | Number   |

| PB0     |     | BUTTON0     |                                                 | 3.3 V    | PIN_H8   |

| PB1     |     | BUTTON1     | High Logic Level when the button is not pressed | 3.3 V    | PIN_C2   |

| PB2     |     | BUTTON2     |                                                 | 3.3 V    | PIN_D4   |

| PB3     |     | BUTTON3     |                                                 | 3.3 V    | PIN_F4   |

Table 2-11 Push-button (HPS fabric) Pin Assignments, Schematic Signal Names

| Board<br>Reference | Schematic<br>Signal<br>Name | Description                                     | I/O<br>Standard | FPGA Pin<br>Number |

|--------------------|-----------------------------|-------------------------------------------------|-----------------|--------------------|

| PB3                | HPS KEY                     | High Logic Level when the button is not pressed | 1.8 V           | PIN_ PIN_B134      |

#### User-Defined Dip Switch

There are four positions slide switches on the FPGA fabric to provide additional FPGA input control. When a position of dip switch is in the DOWN position or the UPPER position, it provides a low logic level or a high logic level to the Agilex SoC FPGA, respectively.

**Table 2-12** lists the signal names and their corresponding Agilex SoC device pin numbers.

Table 2-12 Dip Switch Pin Assignments, Schematic Signal Names, and Functions

| Board     | Schematic   | Description                 | I/O      | FPGA Pin |

|-----------|-------------|-----------------------------|----------|----------|

| Reference | Signal Name | Description                 | Standard | Number   |

| SW0       | SW0         |                             | 3.3 V    | PIN_CK4  |

| SW1       | SW1         | High logic level when SW in | 3.3 V    | PIN_CH4  |

| SW2       | SW2         | the UPPER position.         | 3.3 V    | PIN_K8   |

| SW3       | SW3         |                             | 3.3 V    | PIN_F8   |

#### ■ User-Defined LEDs

The FPGA board consists of 2 FPGA fabric and 1 HPS fabric user-controllable LEDs to allow status and debugging signals to be driven to the LEDs from the designs loaded into the Agilex SoC FPGA. Each LED is driven directly by the FPGA. The LED is turned on or off when the associated pins are driven to a low or high logic level, respectively. A list of the pin names on the FPGA that are connected to the LEDs is given in **Table 2-13**. **Table 2-14** list the information of the LED for the HPS fabric.

Table 2-13 User LEDs (FPGA fabric) Pin Assignments, Schematic Signal Names

| Board<br>Reference | Schematic<br>Signal Name | Description                                         | I/O Standard | FPGA Pin<br>Number |

|--------------------|--------------------------|-----------------------------------------------------|--------------|--------------------|

| LED0               | LED0                     |                                                     | 3.3 V        | PIN_BF120          |

|                    |                          | Driving a logic 0 on the I/O port turns the LED ON. |              |                    |

| LED1               | LED1                     | Driving a logic 1 on the I/O                        | 3.3 V        | PIN_B39            |

| LED2               | LED2                     | port turns the LED OFF.                             | 3.3 V        | PIN_B4             |

| LED3               | LED3                     |                                                     | 3.3 V        | PIN_A11            |

Table 2-14 User LEDs (HPS fabric) Pin Assignments, Schematic Signal Names

| Board     | Schematic   | Description                       | I/O      | FPGA Pin |

|-----------|-------------|-----------------------------------|----------|----------|

| Reference | Signal Name | Description                       | Standard | Number   |

| HPS_LED   | HPS_LED     | Driving a logic 0 on the I/O port | 1.8-V    | PIN_W135 |

|           |             | turns the LED ON.                 |          |          |

|           |             | Driving a logic 1 on the I/O port |          |          |

|           |             | turns the LED OFF.                |          |          |

# 2.6 2x20 GPIO Expansion Header

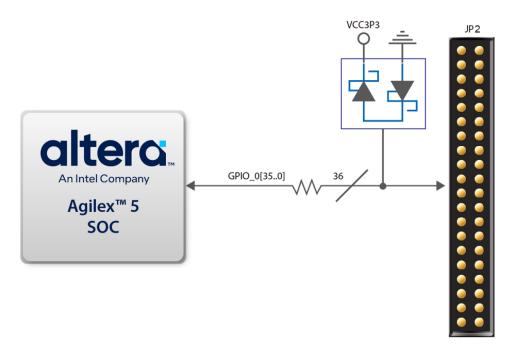

The board has one 40-pin expansion headers. The header has 36 user pins connected directly to the Agilex 5 SoC FPGA. It also comes with DC +5V (VCC5), DC +3.3V (VCC3P3), and two GND pins. The maximum power consumption allowed for a daughter card connected to one GPIO ports is shown in **Table 2-15**.

Table 2-15 Voltage and Max. Current Limit of Expansion Header(s)

| Supplied Voltage | Max. Current Limit |

|------------------|--------------------|

| 5V               | 1A                 |

| 3.3V             | 1.5A               |

Each pin on the expansion headers is connected to two diodes and a resistor for protection against high or low voltage level. Figure 2-14 shows the protection circuitry applied to all 36 data pins. **Table 2-16** shows the pin assignment of the GPIO header.

Figure 2-14 Connections between the GPIO header and Agilex 5 SoC FPGA

**Table 2-16 Pin Assignment of Expansion Headers**

| Schematic   | Description         | I/O      | FPGA Pin |

|-------------|---------------------|----------|----------|

| Signal Name | Description         | Standard | Number   |

| GPIO[0]     | GPIO Connection[0]  | 3.3-V    | PIN_BK31 |

| GPIO[1]     | GPIO Connection[1]  | 3.3-V    | PIN_BU31 |

| GPIO[2]     | GPIO Connection[2]  | 3.3-V    | PIN_BF25 |

| GPIO[3]     | GPIO Connection[3]  | 3.3-V    | PIN_BU28 |

| GPIO[4]     | GPIO Connection[4]  | 3.3-V    | PIN_BR31 |

| GPIO[5]     | GPIO Connection[5]  | 3.3-V    | PIN_BU19 |

| GPIO[6]     | GPIO Connection[6]  | 3.3-V    | PIN_BR19 |

| GPIO[7]     | GPIO Connection[7]  | 3.3-V    | PIN_CJ2  |

| GPIO[8]     | GPIO Connection[8]  | 3.3-V    | PIN_BW28 |

| GPIO[9]     | GPIO Connection[9]  | 3.3-V    | PIN_BW19 |

| GPIO[10]    | GPIO Connection[10] | 3.3-V    | PIN_BU22 |

| GPIO[11]    | GPIO Connection[11] | 3.3-V    | PIN_BR22 |

| GPIO[12]    | GPIO Connection[12] | 3.3-V    | PIN_BM19 |

| GPIO[13]    | GPIO Connection[13] | 3.3-V    | PIN_BM22 |

| GPIO[14]    | GPIO Connection[14] | 3.3-V    | PIN_BK19 |

| GPIO[15]    | GPIO Connection[15] | 3.3-V    | PIN_BK22 |

| GPIO[16]    | GPIO Connection[16] | 3.3-V    | PIN_BH19 |

| GPIO[17]         GPIO Connection[17]         3.3-V         PIN_BR28           GPIO[18]         GPIO Connection[18]         3.3-V         PIN_BM28           GPIO[19]         GPIO Connection[19]         3.3-V         PIN_BM31           GPIO[20]         GPIO Connection[20]         3.3-V         PIN_BK28           GPIO[21]         GPIO Connection[21]         3.3-V         PIN_BH28           GPIO[22]         GPIO Connection[22]         3.3-V         PIN_BF36           GPIO[23]         GPIO Connection[23]         3.3-V         PIN_BF40           GPIO[24]         GPIO Connection[24]         3.3-V         PIN_BF40           GPIO[25]         GPIO Connection[25]         3.3-V         PIN_BF43           GPIO[25]         GPIO Connection[25]         3.3-V         PIN_BP31           GPIO[26]         GPIO Connection[26]         3.3-V         PIN_CK2           GPIO[27]         GPIO Connection[27]         3.3-V         PIN_CF9           GPIO[28]         GPIO Connection[28]         3.3-V         PIN_CF12           GPIO[30]         GPIO Connection[30]         3.3-V         PIN_BF21           GPIO[31]         GPIO Connection[31]         3.3-V         PIN_BE21           GPIO[33]         GPIO Connection[34]         < |          |                     |       |          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------|-------|----------|

| GPIO[19]         GPIO Connection[19]         3.3-V         PIN_BM31           GPIO[20]         GPIO Connection[20]         3.3-V         PIN_BK28           GPIO[21]         GPIO Connection[21]         3.3-V         PIN_BH28           GPIO[22]         GPIO Connection[22]         3.3-V         PIN_BF36           GPIO[23]         GPIO Connection[23]         3.3-V         PIN_BF40           GPIO[24]         GPIO Connection[24]         3.3-V         PIN_BE43           GPIO[25]         GPIO Connection[25]         3.3-V         PIN_BP31           GPIO[26]         GPIO Connection[26]         3.3-V         PIN_CK2           GPIO[27]         GPIO Connection[27]         3.3-V         PIN_CF9           GPIO[28]         GPIO Connection[28]         3.3-V         PIN_CF12           GPIO[29]         GPIO Connection[29]         3.3-V         PIN_BF21           GPIO[30]         GPIO Connection[30]         3.3-V         PIN_BF21           GPIO[31]         GPIO Connection[32]         3.3-V         PIN_BE21           GPIO[33]         GPIO Connection[33]         3.3-V         PIN_BE25           GPIO[34]         GPIO Connection[34]         3.3-V         PIN_BE25                                                          | GPIO[17] | GPIO Connection[17] | 3.3-V | PIN_BR28 |

| GPIO[20]         GPIO Connection[20]         3.3-V         PIN_BK28           GPIO[21]         GPIO Connection[21]         3.3-V         PIN_BH28           GPIO[22]         GPIO Connection[22]         3.3-V         PIN_BF36           GPIO[23]         GPIO Connection[23]         3.3-V         PIN_BF40           GPIO[24]         GPIO Connection[24]         3.3-V         PIN_BE43           GPIO[25]         GPIO Connection[25]         3.3-V         PIN_BP31           GPIO[26]         GPIO Connection[26]         3.3-V         PIN_CK2           GPIO[27]         GPIO Connection[27]         3.3-V         PIN_CF9           GPIO[28]         GPIO Connection[28]         3.3-V         PIN_CF12           GPIO[29]         GPIO Connection[29]         3.3-V         PIN_BF21           GPIO[30]         GPIO Connection[30]         3.3-V         PIN_BF21           GPIO[31]         GPIO Connection[31]         3.3-V         PIN_BF16           GPIO[32]         GPIO Connection[32]         3.3-V         PIN_BE21           GPIO[33]         GPIO Connection[34]         3.3-V         PIN_BE25           GPIO[34]         GPIO Connection[34]         3.3-V         PIN_BE25                                                          | GPIO[18] | GPIO Connection[18] | 3.3-V | PIN_BM28 |

| GPIO[21]         GPIO Connection[21]         3.3-V         PIN_BH28           GPIO[22]         GPIO Connection[22]         3.3-V         PIN_BF36           GPIO[23]         GPIO Connection[23]         3.3-V         PIN_BF40           GPIO[24]         GPIO Connection[24]         3.3-V         PIN_BE43           GPIO[25]         GPIO Connection[25]         3.3-V         PIN_BP31           GPIO[26]         GPIO Connection[26]         3.3-V         PIN_CK2           GPIO[27]         GPIO Connection[27]         3.3-V         PIN_CF9           GPIO[28]         GPIO Connection[28]         3.3-V         PIN_CF12           GPIO[29]         GPIO Connection[29]         3.3-V         PIN_BF21           GPIO[30]         GPIO Connection[30]         3.3-V         PIN_BF21           GPIO[31]         GPIO Connection[31]         3.3-V         PIN_BF16           GPIO[32]         GPIO Connection[32]         3.3-V         PIN_BE21           GPIO[33]         GPIO Connection[33]         3.3-V         PIN_BE25           GPIO[34]         GPIO Connection[34]         3.3-V         PIN_BF29                                                                                                                                        | GPIO[19] | GPIO Connection[19] | 3.3-V | PIN_BM31 |

| GPIO[22]         GPIO Connection[22]         3.3-V         PIN_BF36           GPIO[23]         GPIO Connection[23]         3.3-V         PIN_BF40           GPIO[24]         GPIO Connection[24]         3.3-V         PIN_BE43           GPIO[25]         GPIO Connection[25]         3.3-V         PIN_BP31           GPIO[26]         GPIO Connection[26]         3.3-V         PIN_CK2           GPIO[27]         GPIO Connection[27]         3.3-V         PIN_CF9           GPIO[28]         GPIO Connection[28]         3.3-V         PIN_CH12           GPIO[29]         GPIO Connection[29]         3.3-V         PIN_BF21           GPIO[30]         GPIO Connection[31]         3.3-V         PIN_BF21           GPIO[31]         GPIO Connection[32]         3.3-V         PIN_BE21           GPIO[33]         GPIO Connection[33]         3.3-V         PIN_BE25           GPIO[34]         GPIO Connection[34]         3.3-V         PIN_BF29                                                                                                                                                                                                                                                                                                    | GPIO[20] | GPIO Connection[20] | 3.3-V | PIN_BK28 |

| GPIO[23]         GPIO Connection[23]         3.3-V         PIN_BF40           GPIO[24]         GPIO Connection[24]         3.3-V         PIN_BE43           GPIO[25]         GPIO Connection[25]         3.3-V         PIN_BP31           GPIO[26]         GPIO Connection[26]         3.3-V         PIN_CK2           GPIO[27]         GPIO Connection[27]         3.3-V         PIN_CF9           GPIO[28]         GPIO Connection[28]         3.3-V         PIN_CH12           GPIO[29]         GPIO Connection[29]         3.3-V         PIN_CF12           GPIO[30]         GPIO Connection[30]         3.3-V         PIN_BF21           GPIO[31]         GPIO Connection[31]         3.3-V         PIN_BF16           GPIO[32]         GPIO Connection[32]         3.3-V         PIN_BE21           GPIO[33]         GPIO Connection[33]         3.3-V         PIN_BE25           GPIO[34]         GPIO Connection[34]         3.3-V         PIN_BF29                                                                                                                                                                                                                                                                                                    | GPIO[21] | GPIO Connection[21] | 3.3-V | PIN_BH28 |

| GPIO[24]         GPIO Connection[24]         3.3-V         PIN_BE43           GPIO[25]         GPIO Connection[25]         3.3-V         PIN_BP31           GPIO[26]         GPIO Connection[26]         3.3-V         PIN_CK2           GPIO[27]         GPIO Connection[27]         3.3-V         PIN_CF9           GPIO[28]         GPIO Connection[28]         3.3-V         PIN_CH12           GPIO[29]         GPIO Connection[29]         3.3-V         PIN_CF12           GPIO[30]         GPIO Connection[30]         3.3-V         PIN_BF21           GPIO[31]         GPIO Connection[31]         3.3-V         PIN_BF16           GPIO[32]         GPIO Connection[32]         3.3-V         PIN_BE21           GPIO[33]         GPIO Connection[33]         3.3-V         PIN_BE25           GPIO[34]         GPIO Connection[34]         3.3-V         PIN_BF29                                                                                                                                                                                                                                                                                                                                                                                  | GPIO[22] | GPIO Connection[22] | 3.3-V | PIN_BF36 |

| GPIO[25]         GPIO Connection[25]         3.3-V         PIN_BP31           GPIO[26]         GPIO Connection[26]         3.3-V         PIN_CK2           GPIO[27]         GPIO Connection[27]         3.3-V         PIN_CF9           GPIO[28]         GPIO Connection[28]         3.3-V         PIN_CH12           GPIO[29]         GPIO Connection[29]         3.3-V         PIN_CF12           GPIO[30]         GPIO Connection[30]         3.3-V         PIN_BF21           GPIO[31]         GPIO Connection[31]         3.3-V         PIN_BF16           GPIO[32]         GPIO Connection[32]         3.3-V         PIN_BE21           GPIO[33]         GPIO Connection[33]         3.3-V         PIN_BE25           GPIO[34]         GPIO Connection[34]         3.3-V         PIN_BF29                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GPIO[23] | GPIO Connection[23] | 3.3-V | PIN_BF40 |

| GPIO[26]         GPIO Connection[26]         3.3-V         PIN_CK2           GPIO[27]         GPIO Connection[27]         3.3-V         PIN_CF9           GPIO[28]         GPIO Connection[28]         3.3-V         PIN_CH12           GPIO[29]         GPIO Connection[29]         3.3-V         PIN_CF12           GPIO[30]         GPIO Connection[30]         3.3-V         PIN_BF21           GPIO[31]         GPIO Connection[31]         3.3-V         PIN_BF16           GPIO[32]         GPIO Connection[32]         3.3-V         PIN_BE21           GPIO[33]         GPIO Connection[33]         3.3-V         PIN_BE25           GPIO[34]         GPIO Connection[34]         3.3-V         PIN_BF29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | GPIO[24] | GPIO Connection[24] | 3.3-V | PIN_BE43 |

| GPIO[27]         GPIO Connection[27]         3.3-V         PIN_CF9           GPIO[28]         GPIO Connection[28]         3.3-V         PIN_CH12           GPIO[29]         GPIO Connection[29]         3.3-V         PIN_CF12           GPIO[30]         GPIO Connection[30]         3.3-V         PIN_BF21           GPIO[31]         GPIO Connection[31]         3.3-V         PIN_BF16           GPIO[32]         GPIO Connection[32]         3.3-V         PIN_BE21           GPIO[33]         GPIO Connection[33]         3.3-V         PIN_BE25           GPIO[34]         GPIO Connection[34]         3.3-V         PIN_BF29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | GPIO[25] | GPIO Connection[25] | 3.3-V | PIN_BP31 |

| GPIO[28]         GPIO Connection[28]         3.3-V         PIN_CH12           GPIO[29]         GPIO Connection[29]         3.3-V         PIN_CF12           GPIO[30]         GPIO Connection[30]         3.3-V         PIN_BF21           GPIO[31]         GPIO Connection[31]         3.3-V         PIN_BF16           GPIO[32]         GPIO Connection[32]         3.3-V         PIN_BE21           GPIO[33]         GPIO Connection[33]         3.3-V         PIN_BE25           GPIO[34]         GPIO Connection[34]         3.3-V         PIN_BF29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | GPIO[26] | GPIO Connection[26] | 3.3-V | PIN_CK2  |

| GPIO[29]         GPIO Connection[29]         3.3-V         PIN_CF12           GPIO[30]         GPIO Connection[30]         3.3-V         PIN_BF21           GPIO[31]         GPIO Connection[31]         3.3-V         PIN_BF16           GPIO[32]         GPIO Connection[32]         3.3-V         PIN_BE21           GPIO[33]         GPIO Connection[33]         3.3-V         PIN_BE25           GPIO[34]         GPIO Connection[34]         3.3-V         PIN_BF29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | GPIO[27] | GPIO Connection[27] | 3.3-V | PIN_CF9  |

| GPIO[30]         GPIO Connection[30]         3.3-V         PIN_BF21           GPIO[31]         GPIO Connection[31]         3.3-V         PIN_BF16           GPIO[32]         GPIO Connection[32]         3.3-V         PIN_BE21           GPIO[33]         GPIO Connection[33]         3.3-V         PIN_BE25           GPIO[34]         GPIO Connection[34]         3.3-V         PIN_BF29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | GPIO[28] | GPIO Connection[28] | 3.3-V | PIN_CH12 |

| GPIO[31]         GPIO Connection[31]         3.3-V         PIN_BF16           GPIO[32]         GPIO Connection[32]         3.3-V         PIN_BE21           GPIO[33]         GPIO Connection[33]         3.3-V         PIN_BE25           GPIO[34]         GPIO Connection[34]         3.3-V         PIN_BF29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | GPIO[29] | GPIO Connection[29] | 3.3-V | PIN_CF12 |

| GPIO[32]         GPIO Connection[32]         3.3-V         PIN_BE21           GPIO[33]         GPIO Connection[33]         3.3-V         PIN_BE25           GPIO[34]         GPIO Connection[34]         3.3-V         PIN_BF29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GPIO[30] | GPIO Connection[30] | 3.3-V | PIN_BF21 |

| GPIO[33]         GPIO Connection[33]         3.3-V         PIN_BE25           GPIO[34]         GPIO Connection[34]         3.3-V         PIN_BF29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | GPIO[31] | GPIO Connection[31] | 3.3-V | PIN_BF16 |

| GPIO[34] GPIO Connection[34] 3.3-V PIN_BF29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | GPIO[32] | GPIO Connection[32] | 3.3-V | PIN_BE21 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GPIO[33] | GPIO Connection[33] | 3.3-V | PIN_BE25 |

| GPIO[35]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | GPIO[34] | GPIO Connection[34] | 3.3-V | PIN_BF29 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | GPIO[35] | GPIO Connection[35] | 3.3-V | PIN_BE29 |

# 2.7 Micro SD Card and eMMC

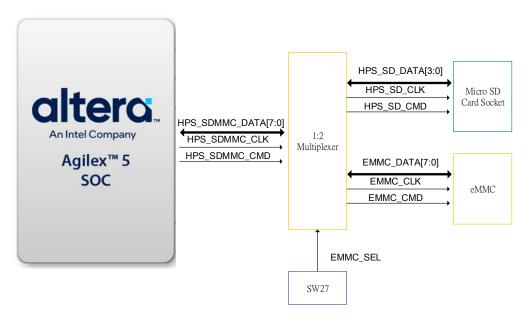

The board provides Micro SD Card and on-board eMMC device (SanDisk 8GB:SDINBDG4-8G) for HPS fabric in the FPGA (See Figure 2-15). Users can choose one of them for HPS boot/data/system storage. The switch SW27(See Figure 2-16) on the board can help the user select which device (Micro SD Card or eMMC) will be used for HPS fabric. The Micro SD card socket can provide flexible capacity expansion while eMMC device can support stable and fixed storage solutions. **Table 2-17** lists the pin assignment of Micro SD card socket and eMMC device to the HPS.

Figure 2-15 Pin-out of Micro SD Card socket

Figure 2-16 Pin-out of Micro SD Card socket

Table 2-17 Micro SD Card Socket Header Pin Assignments, Schematic Signal Names, and Functions

| Schematic         | Description              | I/O      | FPGA Pin  |

|-------------------|--------------------------|----------|-----------|

| Signal Name       | Description              | Standard | Number    |

| HPS_SDMMC_CLK     | HPS SD/eMMC Clock        | 1.8-V    | PIN_D132  |

| HPS_SDMMC_CMD     | HPS SD/eMMC Command Line | 1.8-V    | PIN_AB132 |

| HPS_SDMMC_DATA[0] | HPS SD/eMMC Data[0]      | 1.8-V    | PIN_E135  |

| HPS_SDMMC_DATA[1] | HPS SD/eMMC Data[1]      | 1.8-V    | PIN_F132  |

| HPS_SDMMC_DATA[2] | HPS SD/eMMC Data[2] | 1.8-V | PIN_AA135 |

|-------------------|---------------------|-------|-----------|

| HPS_SDMMC_DATA[3] | HPS SD/eMMC Data[3] | 1.8-V | PIN_V127  |

| HPS_SDMMC_DATA[4] | HPS SD/eMMC Data[4] | 1.8-V | PIN_T127  |

| HPS_SDMMC_DATA[5] | HPS SD/eMMC Data[5] | 1.8-V | PIN_Y132  |

| HPS_SDMMC_DATA[6] | HPS SD/eMMC Data[6] | 1.8-V | PIN_T124  |

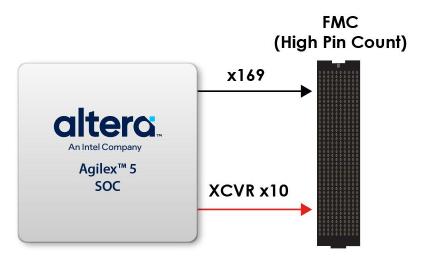

#### 2.8 FMC+ Connector

The board equipped with a FPGA Mezzanine Card Plus(FMC+) connector to provide a mechanism to extend the peripheral-set of an FPGA host board by means of add-on daughter cards, which can address today's high-speed signaling requirements as well as low-speed device interface support. The FMC+ interfaces support JTAG, clock outputs and inputs, high-speed serial I/O (transceivers), and single-ended or differential signaling.

There FMC+ connector on the Atum A5 board is a **High Pin Count (HPC)** size of connector, The HPC connector on Atum A5 board can provides 169 user-define, single-ended signals (80 pair differential I/O) and 12 serial transceiver pairs. **Figure 2-17** is the FPGA I/O connected to the FMC+ connector on the Atum A5 board.

Below we will introduce according to the individual functions of FMC+ connector.

Figure 2-17 FMC+ connector on Atum A5 board

#### ■ Clock Interface

Table 2-18 shows the FPGA clock interface pin placement on the FMC+ connector.

Table 2-18 FMC+ clock input interface distribution

|                 |                     |                      | FPGA       |

|-----------------|---------------------|----------------------|------------|

| Signal Name     | FMC Clock input pin | FPGA Clock Input Pin | Pin        |

|                 | name                | Placement            | Assignment |

| FMCP_CLK_M2C_p0 | CLK0_M2C_P          | CLK_B_2B_0P          | PIN_CH38   |

| FMCP_CLK_M2C_n0 | CLK0_M2C_N          | CLK_B_2B_0N          | PIN_CF38   |

| FMCP_CLK_M2C_p1 | CLK1_M2C_P          | CLK_B_2A_1P          | PIN_BM92   |

| FMCP_CLK_M2C_n1 | CLK1_M2C_N          | CLK_B_2A_1N          | PIN_BP92   |

| FMCP_HA_p1      | HA01_P_CC           | CLK_T_2A_1P          | PIN_BF75   |

| FMCP_HA_n1      | HA01_N_CC           | CLK_T_2A_1N          | PIN_BM71   |

| FMCP_HA_p17     | HA17_P              | CLK_T_2A_0P          | PIN_BP71   |

| FMCP_HA_n17     | HA17_N              | CLK_T_2A_0N          | PIN_BF72   |

| FMCP_HB_p1      | HB01_P              | CLK_B_2A_0P          | PIN_BU78   |

| FMCP_HB_n1      | HB01_N              | CLK_B_2A_0N          | PIN_CA78   |

| FMCP_LA_p0      | LA00_P_CC           | CLK_T_2B_0P          | PIN_BK38   |

| FMCP_LA_n0      | LA00_N_CC           | CLK_T_2B_0N          | PIN_BM38   |

| FMCP_LA_p17     | LA17_P_CC           | CLK_B_2B_1P          | PIN_BR49   |

| FMCP_LA_n17     | LA17_N_CC           | CLK_B_2B_1N          | PIN_BU49   |

#### Power Supply

The Atum A5 board provides 12V, 3.3V and 1.2V(VADJ) power through FMC+ ports. **Table 2-19** indicates the maximum power consumption for the FMC+ connector.

CAUTION: Before powering on the Atum A5 board with a daughter card, please check to see if there is a short circuit between the power pins and FMC+ FPGA I/O.

Table 2-19 Power Supply of the FMC+

| Supplied Voltage | Max. Current Limit |

|------------------|--------------------|

| 12V              | 1A                 |

| 3.3V             | 3A                 |

| 1.2V(VADJ)       | 4A                 |

#### **■** JTAG Chain on FMC+

The JTAG chain on the Atum A5 board supports JTAG interface extension to the FMC+ connector so that the JTAG device on the user's FMC+ daughter card can be joined with JTAG chain on the Atum A5 board. Users can enable this feature through the switch (**SW31**) on the Atum A5 board. In the board's default setting, the JTAG interface of the FMC+ connector is bypassed to keep the Atum A5 board JTAG chain to maintain close loop. For detailed setting, please refer to **Section 2.2: FMC+ JTAG Interface Switch**.

#### ■ Adjustable I/O Standards

Some of the FPGA pin's I/O standard connected with the HPC (High Pin Count) part of the FMC+ connector can be set to voltages: 1.2V and 1.3V. This function can be achieved because the VCCIO power pin of the FPGA bank where these FPGA I/Os are located can adjust the input voltage through the 3 pin header (JP1). For detailed setting, please refer to Section 2.2: **FMC+ HAB VCCIO Select Header**.

#### ■ Transceiver Channels Speed

There are 12 E-series GTS transceivers connected to the Agilex SoC FPGA on the FMC+ connector and the maximum transmission speed is **16 G bps**.

#### Component Information of the FMC+ Connector

**Table 2-20** shows the manufacture and part numbers of the FMC connector.

Table 2-20 FMC+ Connector Part Number on the Atum A5 board

| Connector        | Manufacturer and | Part Number |

|------------------|------------------|-------------|

| FMC+ on the Atum | Samtoo : ASD 1   | 194220 04   |

| A5 board         | Samtec : ASP-1   | 164329-01   |

| Mating Connector | Samtec : ASP-1   | 184330-01   |

#### ■ Refernce clock for FMC+ transceivers

There are three clocks are feed to the FPGA for the FMC+ transceivers as the reference clock. These clocks are provides by the programmable clock generator(SI5391B). User can modify the clock frequencies via I2C interface for differential applications.

Table 2-21 FMC+ Reference clock

| Course   | Schematic      | Default   | I/O      | Agilex Pin |

|----------|----------------|-----------|----------|------------|

| Source   | Signal Name    | Frequency | Standard | Number     |

| U57.OUT3 | FMCP_REFCLK0_p | 148.5 MHz | LVDS     | PIN_ BP8   |

| U57.OUT4 | FMCP_REFCLK1_p | 135 MHz   | LVDS     | PIN_A24    |

| U57.OUT5 | FMCP_REFCLK2_p | 100MHz    | LVDS     | PIN_BW7    |

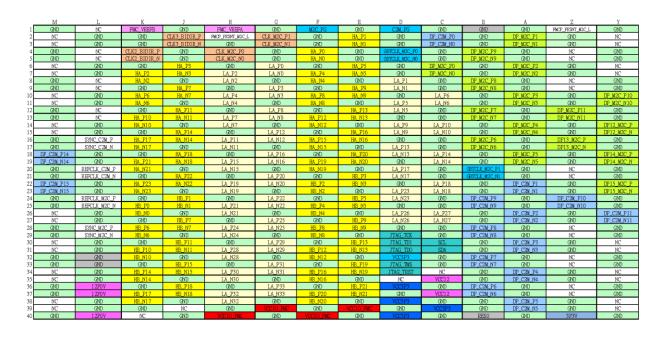

#### **■** FPGA Pin Assignments for FMC+ Connector

Figure 2-18 shows the pin out table of the FMC+ connector on the Atum A5 and 錯誤! 找不到參照來源。 lists the FMC+ connector pin assignments, signal names and functions.

Figure 2-18 FMC+ pin out table

Table 2-22 FMC+ Connector Pin Assignments, Signal Names and Functions

| Signal Name       | FPGA Pin<br>Number | Description   | I/O Standard |

|-------------------|--------------------|---------------|--------------|

| FMCP_CLK2_BIDIR_p | PIN_CF49           | FMCP data bus | 1.2 V        |

| FMCP_CLK2_BIDIR_n | PIN_CH49           | FMCP data bus | 1.2 V        |

| FMCP_CLK3_BIDIR_p | PIN_BW49           | FMCP data bus | 1.2 V        |

| FMCP_CLK3_BIDIR_n | PIN_CA49           | FMCP data bus | 1.2 V        |

34

| FMCP_CLK_M2C_p[0] | PIN_CH38 | Clock from mezzanine module to carrier card positive 0 | True Differential Signaling |

|-------------------|----------|--------------------------------------------------------|-----------------------------|

| FMCP_CLK_M2C_n[0] | PIN_CF38 | Clock from mezzanine module to carrier card negative 0 | True Differential Signaling |

| FMCP_CLK_M2C_p[1] | PIN_BP92 | Clock from mezzanine module to carrier card positive 1 | True Differential Signaling |

| FMCP_CLK_M2C_n[1] | PIN_BM92 | Clock from mezzanine module to carrier card negative 1 | True Differential Signaling |

| FMCP_HA_p[0]      | PIN_BM69 | FMCP HA bank<br>data p0                                | 1.2 V/1.3 *(1)              |

| FMCP_HA_p[1]      | PIN_BM71 | FMCP HA bank<br>data p1                                | 1.2 V/1.3                   |

| FMCP_HA_p[2]      | PIN_BH62 | FMCP HA bank<br>data p2                                | 1.2 V/1.3                   |

| FMCP_HA_p[3]      | PIN_BR69 | FMCP HA bank<br>data p3                                | 1.2 V/1.3                   |

| FMCP_HA_p[4]      | PIN_BW69 | FMCP HA bank<br>data p4                                | 1.2 V/1.3                   |

| FMCP_HA_p[5]      | PIN_BU59 | FMCP HA bank<br>data p5                                | 1.2 V/1.3                   |

| FMCP_HA_p[6]      | PIN_BH69 | FMCP HA bank<br>data p6                                | 1.2 V/1.3                   |

| FMCP_HA_p[7]      | PIN_CH69 | FMCP HA bank<br>data p7                                | 1.2 V/1.3                   |

| FMCP_HA_p[8]      | PIN_CF59 | FMCP HA bank                                           | 1.2 V/1.3                   |

|               |          | data p8                  |           |

|---------------|----------|--------------------------|-----------|

| FMCP_HA_p[9]  | PIN_BW59 | FMCP HA bank<br>data p9  | 1.2 V/1.3 |

| FMCP_HA_p[10] | PIN_CA62 | FMCP HA bank<br>data p10 | 1.2 V/1.3 |

| FMCP_HA_p[11] | PIN_BM59 | FMCP HA bank<br>data p11 | 1.2 V/1.3 |

| FMCP_HA_p[12] | PIN_BM62 | FMCP HA bank<br>data p12 | 1.2 V/1.3 |

| FMCP_HA_p[13] | PIN_CF62 | FMCP HA bank<br>data p13 | 1.2 V/1.3 |

| FMCP_HA_p[14] | PIN_CC71 | FMCP HA bank<br>data p14 | 1.2 V/1.3 |

| FMCP_HA_p[15] | PIN_CF71 | FMCP HA bank<br>data p15 | 1.2 V/1.3 |

| FMCP_HA_p[16] | PIN_BU62 | FMCP HA bank<br>data p16 | 1.2 V/1.3 |

| FMCP_HA_p[17] | PIN_BF75 | FMCP HA bank<br>data p17 | 1.2 V/1.3 |

| FMCP_HA_p[18] | PIN_BE83 | FMCP HA bank<br>data p18 | 1.2 V/1.3 |

| FMCP_HA_p[19] | PIN_BE79 | FMCP HA bank<br>data p19 | 1.2 V/1.3 |

| FMCP_HA_p[20] | PIN_BR71 | FMCP HA bank<br>data p20 | 1.2 V/1.3 |

| FMCP_HA_p[21] | PIN_BF93 | FMCP HA bank<br>data p21 | 1.2 V/1.3 |

| FMCP_HA_p[22] | PIN_BF86 | FMCP HA bank<br>data p22 | 1.2 V/1.3 |

| FMCP_HA_p[23] | PIN_BE96 | FMCP HA bank<br>data p23 | 1.2 V/1.3 |

| FMCP_HA_n[0]  | PIN_BK69 | FMCP HA bank             | 1.2 V/1.3 |

|               |          | data n0                  |           |

|---------------|----------|--------------------------|-----------|

| FMCP_HA_n[1]  | PIN_BP71 | FMCP HA bank<br>data n1  | 1.2 V/1.3 |

| FMCP_HA_n[2]  | PIN_BH59 | FMCP HA bank<br>data n2  | 1.2 V/1.3 |

| FMCP_HA_n[3]  | PIN_BU69 | FMCP HA bank<br>data n3  | 1.2 V/1.3 |

| FMCP_HA_n[4]  | PIN_CA69 | FMCP HA bank<br>data n4  | 1.2 V/1.3 |

| FMCP_HA_n[5]  | PIN_BR59 | FMCP HA bank<br>data n5  | 1.2 V/1.3 |

| FMCP_HA_n[6]  | PIN_BH71 | FMCP HA bank<br>data n6  | 1.2 V/1.3 |

| FMCP_HA_n[7]  | PIN_CF69 | FMCP HA bank<br>data n7  | 1.2 V/1.3 |

| FMCP_HA_n[8]  | PIN_CH59 | FMCP HA bank<br>data n8  | 1.2 V/1.3 |

| FMCP_HA_n[9]  | PIN_CA59 | FMCP HA bank<br>data n9  | 1.2 V/1.3 |

| FMCP_HA_n[10] | PIN_CC62 | FMCP HA bank<br>data n10 | 1.2 V/1.3 |

| FMCP_HA_n[11] | PIN_BK59 | FMCP HA bank<br>data n11 | 1.2 V/1.3 |

| FMCP_HA_n[12] | PIN_BP62 | FMCP HA bank<br>data n12 | 1.2 V/1.3 |

| FMCP_HA_n[13] | PIN_CH62 | FMCP HA bank<br>data n13 | 1.2 V/1.3 |

| FMCP_HA_n[14] | PIN_CA71 | FMCP HA bank<br>data n14 | 1.2 V/1.3 |

| FMCP_HA_n[15] | PIN_CH71 | FMCP HA bank<br>data n15 | 1.2 V/1.3 |

| FMCP_HA_n[16] | PIN_BR62 | FMCP HA bank             | 1.2 V/1.3 |

|               |          | data n16                 |           |

|---------------|----------|--------------------------|-----------|

| FMCP_HA_n[17] | PIN_BF72 | FMCP HA bank<br>data n17 | 1.2 V/1.3 |

| FMCP_HA_n[18] | PIN_BF83 | FMCP HA bank<br>data n18 | 1.2 V/1.3 |

| FMCP_HA_n[19] | PIN_BE75 | FMCP HA bank<br>data n19 | 1.2 V/1.3 |

| FMCP_HA_n[20] | PIN_BU71 | FMCP HA bank<br>data n20 | 1.2 V/1.3 |

| FMCP_HA_n[21] | PIN_BF90 | FMCP HA bank<br>data n21 | 1.2 V/1.3 |

| FMCP_HA_n[22] | PIN_BE86 | FMCP HA bank<br>data n22 | 1.2 V/1.3 |

| FMCP_HA_n[23] | PIN_BE93 | FMCP HA bank<br>data n23 | 1.2 V/1.3 |

| FMCP_HB_p[0]  | PIN_BR81 | FMCP HB bank<br>data p0  | 1.2 V/1.3 |

| FMCP_HB_p[1]  | PIN_BW78 | FMCP HB bank<br>data p1  | 1.2 V/1.3 |

| FMCP_HB_p[2]  | PIN_CL91 | FMCP HB bank<br>data p2  | 1.2 V/1.3 |

| FMCP_HB_p[3]  | PIN_BM81 | FMCP HB bank<br>data p3  | 1.2 V/1.3 |

| FMCP_HB_p[4]  | PIN_BK89 | FMCP HB bank<br>data p4  | 1.2 V/1.3 |

| FMCP_HB_p[5]  | PIN_CF81 | FMCP HB bank<br>data p5  | 1.2 V/1.3 |

| FMCP_HB_p[6]  | PIN_BR92 | FMCP HB bank<br>data p6  | 1.2 V/1.3 |

| FMCP_HB_p[7]  | PIN_BH89 | FMCP HB bank<br>data p7  | 1.2 V/1.3 |

| FMCP_HB_p[8]  | PIN_CH89 | FMCP HB bank             | 1.2 V/1.3 |

|               |          | data p8                  |           |

|---------------|----------|--------------------------|-----------|

| FMCP_HB_p[9]  | PIN_CK97 | FMCP HB bank<br>data p9  | 1.2 V/1.3 |

| FMCP_HB_p[10] | PIN_CL88 | FMCP HB bank<br>data p10 | 1.2 V/1.3 |

| FMCP_HB_p[11] | PIN_BR89 | FMCP HB bank<br>data p11 | 1.2 V/1.3 |

| FMCP_HB_p[12] | PIN_CH78 | FMCP HB bank<br>data p12 | 1.2 V/1.3 |

| FMCP_HB_p[13] | PIN_BR78 | FMCP HB bank<br>data p13 | 1.2 V/1.3 |

| FMCP_HB_p[14] | PIN_CK76 | FMCP HB bank<br>data p14 | 1.2 V/1.3 |

| FMCP_HB_p[15] | PIN_CK85 | FMCP HB bank<br>data p15 | 1.2 V/1.3 |

| FMCP_HB_p[16] | PIN_CA81 | FMCP HB bank<br>data p16 | 1.2 V/1.3 |

| FMCP_HB_p[17] | PIN_BM78 | FMCP HB bank<br>data p17 | 1.2 V/1.3 |

| FMCP_HB_p[18] | PIN_BH81 | FMCP HB bank<br>data p18 | 1.2 V/1.3 |

| FMCP_HB_p[19] | PIN_CK80 | FMCP HB bank<br>data p19 | 1.2 V/1.3 |

| FMCP_HB_p[20] | PIN_CC92 | FMCP HB bank<br>data p20 | 1.2 V/1.3 |

| FMCP_HB_p[21] | PIN_CF92 | FMCP HB bank<br>data p21 | 1.2 V/1.3 |

| FMCP_HB_n[0]  | PIN_BU81 | FMCP HB bank<br>data n0  | 1.2 V/1.3 |

| FMCP_HB_n[1]  | PIN_CA78 | FMCP HB bank<br>data n1  | 1.2 V/1.3 |

| FMCP_HB_n[2]  | PIN_CK94 | FMCP HB bank             | 1.2 V/1.3 |

|               |          | data n2                  |           |

|---------------|----------|--------------------------|-----------|

| FMCP_HB_n[3]  | PIN_BP81 | FMCP HB bank<br>data n3  | 1.2 V/1.3 |

| FMCP_HB_n[4]  | PIN_BM89 | FMCP HB bank<br>data n4  | 1.2 V/1.3 |

| FMCP_HB_n[5]  | PIN_CH81 | FMCP HB bank<br>data n5  | 1.2 V/1.3 |

| FMCP_HB_n[6]  | PIN_BU92 | FMCP HB bank<br>data n6  | 1.2 V/1.3 |

| FMCP_HB_n[7]  | PIN_BH92 | FMCP HB bank<br>data n7  | 1.2 V/1.3 |

| FMCP_HB_n[8]  | PIN_CF89 | FMCP HB bank<br>data n8  | 1.2 V/1.3 |

| FMCP_HB_n[9]  | PIN_CL97 | FMCP HB bank<br>data n9  | 1.2 V/1.3 |

| FMCP_HB_n[10] | PIN_CK88 | FMCP HB bank<br>data n10 | 1.2 V/1.3 |

| FMCP_HB_n[11] | PIN_BU89 | FMCP HB bank<br>data n11 | 1.2 V/1.3 |

| FMCP_HB_n[12] | PIN_CF78 | FMCP HB bank<br>data n12 | 1.2 V/1.3 |

| FMCP_HB_n[13] | PIN_BU78 | FMCP HB bank<br>data n13 | 1.2 V/1.3 |

| FMCP_HB_n[14] | PIN_CL76 | FMCP HB bank<br>data n14 | 1.2 V/1.3 |

| FMCP_HB_n[15] | PIN_CL85 | FMCP HB bank<br>data n15 | 1.2 V/1.3 |

| FMCP_HB_n[16] | PIN_CC81 | FMCP HB bank<br>data n16 | 1.2 V/1.3 |

| FMCP_HB_n[17] | PIN_BK78 | FMCP HB bank<br>data n17 | 1.2 V/1.3 |

| FMCP_HB_n[18] | PIN_BH78 | FMCP HB bank             | 1.2 V/1.3 |

|               |          | data n18                 |           |

|---------------|----------|--------------------------|-----------|

|               |          | uata 1110                |           |

| FMCP_HB_n[19] | PIN_CL82 | FMCP HB bank<br>data n19 | 1.2 V/1.3 |

| FMCP_HB_n[20] | PIN_CA92 | FMCP HB bank<br>data n20 | 1.2 V/1.3 |